## WESTERN DIGITAL

## C O R P O R A T I O N

## O.E.M. MANUAL

## WD7000-ASC HOST BUS ADAPTER

## DOC.# 79-000124

# COPYRIGHT © 1987 WESTERN DIGITAL CORP.

## ALL RIGHTS RESERVED

This document is protected by copyright, and contains information proprietary to Western Digital Corporation. Any copying, adaptation, distribution, public performance, or public display of this document without the expressed written consent of Western Digital Corporation is strictly prohibited. The receipt or possession of this document does not convey any rights to reproduce or distribute its contents, or to manufacture, use, or sell anything that it may describe, in whole or in part, without the specific consent of Western Digital Corporation.

## TABLE OF CONTENTS

| SECTION | 1 II | NTRODUCTION                                                                                                                                                                                                                                                                                                                                | PAGE                                                                             |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|         | 1.0  | Document Scope                                                                                                                                                                                                                                                                                                                             | 1-1                                                                              |

|         | 1.1  | Description                                                                                                                                                                                                                                                                                                                                | 1-1                                                                              |

|         | 1.2  | Features                                                                                                                                                                                                                                                                                                                                   | 1-3                                                                              |

|         | 1.3  | Operation<br>1.3.1 Local Microprocessor (LCPU)<br>1.3.1.1 LCPU Clock<br>1.3.2 Program Memory<br>1.3.3 Scratchpad RAM<br>1.3.4 First Party DMA Logic<br>1.3.5 Host Interface Logic<br>1.3.6 SCSI Bus Interface Controller<br>1.3.7 Floppy Disk Subsystem Controller<br>1.3.8 BIOS ROM<br>1.3.9 Control Support Logic<br>1.3.9.1 Reset Logic | 1-4<br>1-6<br>1-6<br>1-6<br>1-7<br>1-7<br>1-7<br>1-7<br>1-8<br>1-8<br>1-8<br>1-8 |

| SECTION | 2 SI | PECIFICATIONS                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|         | 2.0  | General                                                                                                                                                                                                                                                                                                                                    | 2-1                                                                              |

|         | 2.1  | Physical                                                                                                                                                                                                                                                                                                                                   | 2-1                                                                              |

|         | 2.2  | Power                                                                                                                                                                                                                                                                                                                                      | 2-1                                                                              |

|         | 2.3  | Performance                                                                                                                                                                                                                                                                                                                                | 2-1                                                                              |

|         | 2.4  | Host Interface                                                                                                                                                                                                                                                                                                                             | 2-2                                                                              |

|         | 2.5  | SCSI Interface                                                                                                                                                                                                                                                                                                                             | 2-2                                                                              |

|         | 2.6  | Environmental                                                                                                                                                                                                                                                                                                                              | 2-2                                                                              |

.

| 3 | .0 | General               | 3  | -1 |

|---|----|-----------------------|----|----|

| 3 | .1 | Hardware Installation | 3  | -1 |

| 3 | .2 | Software Installation | '3 | -1 |

| 3 | .3 | Jumper Configuration  | 3  | -1 |

PAGE

## SECTION 4 INTERFACE CONNECTIONS

| 4.0 | General |                                      | 4-1   |

|-----|---------|--------------------------------------|-------|

| 4.1 | Host In | terface Connectors (P1, P2)          | 4-1   |

|     | 4.1.1   | Data Bus $(D7 - D0)$                 | 4-3   |

|     |         | Address Enable (AEN)                 | 4-3   |

|     |         | Address Bus (A19 A0)                 | 4-4   |

|     | 4.1.4   | Buffered Address Latch Enable (BALE) | 4-4   |

|     | 4.1.5   | Memory Read (MEMR)                   | 4-4   |

|     | 4.1.6   | Memory Write (MEMW )                 | 4 - 4 |

|     | 4.1.7   | I/O Read (IOR)                       | 4-4   |

|     |         | I/O Write (IOW)                      | 4-4   |

|     | 4.1.9   |                                      | 4-5   |

|     | 4.1.10  | Reset (RESET DRV)                    | 4-5   |

|     | 4.1.11  | I/O Channel Ready (IOCHRDY)          | 4-5   |

|     | 4.1.12  | I/O Channel Check (IOCHCHK)          | 4-5   |

|     | 4.1.13  | Zero Wait State (OWS)                | 4-5   |

|     | 4.1.14  |                                      | 4-5   |

|     |         | System Clock (CLK)                   | 4-5   |

|     | 4.1.16  | Oscillator Clock (OSC)               | 4-5   |

|     |         | Terminal Count (TC)                  | 4-6   |

|     | 4.1.18  | +5VDC (B3, B29, D16)                 | 4-6   |

|     | 4.1.19  | -12VDC (B7)                          | 4-6   |

|     |         | +12VDC (B9)                          | 4-6   |

|     | 4.1.21  | Ground (B1, B10, B31, D18)           | 4-6   |

|     | 4.1.22  |                                      | 4-6   |

|     | 4.1.23  | DMA Data Request (DRQ5 to DRQ7)      | 4-6   |

|     | 4.1.24  | Data Acknowledge (DACK5 to DACK7)    | 4-7   |

|     |         | Interrupt Request (IRQX)             | 4-7   |

|     | 4.1.26  | Memory Chip Select 16-Bit (MEMCS16 ) | 4-7   |

|     | 4.1.27  | I/O Chip Select 16-Bit (IOCS16)      | 4-7   |

|     | 4.1.28  | System Bus High Enable (SBHE)        | 4-7   |

|     | 4.1.29  | Data Bus (D15 - D0)                  | 4-7   |

|     |         | Unlatched Address Bus (LA23-LA17)    | 4-7   |

|     |         |                                      |       |

| SECTION | 4 I  | NTERFACE CONNECTIONS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PAGE                                                                                           |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|         | 4.2  | SCSI Interface Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-8                                                                                            |

|         | 4.3  | Floppy Disk Drive Interface Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-8                                                                                            |

| SECTION | 5 II | NTERFACE PROTOCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PAGE                                                                                           |

|         | 5.0  | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-1                                                                                            |

|         | 5.1  | General Signal Flow<br>5.1.1 Power-Up Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-1<br>5-3                                                                                     |

|         | 5.2  | <pre>Host Hardware Interface<br/>5.2.1 Status Port<br/>5.2.1.1 Interrupt Image Flag (D7)<br/>5.2.1.2 Command Port Ready (D6)<br/>5.2.1.3 Command Byte Rejection (D5)<br/>5.2.1.4 WD7000-ASC Initialization Flag (D4)<br/>5.2.2 Interrupt Status Byte<br/>5.2.3 Command Port<br/>5.2.4 Interrupt Acknowledge<br/>5.2.5 Host Control Register<br/>5.2.5.1 WD7000-ASC Reset (D0)<br/>5.2.5.2 SCSI Reset (D1)<br/>5.2.5.3 DMA Request Enable (D2)<br/>5.2.5.4 Interrupt Request Enable (D3)</pre> | 5-3<br>5-4<br>5-4<br>5-5<br>5-5<br>5-5<br>5-6<br>5-6<br>5-6<br>5-7<br>5-7<br>5-7<br>5-8<br>5-8 |

|         | 5.3  | Mail Boxes<br>5.3.1 Outgoing Mail<br>5.3.2 Incoming Mail<br>5.3.2.1 ICMB Return Status                                                                                                                                                                                                                                                                                                                                                                                                        | 5-8<br>5-9<br>5-10<br>5-10                                                                     |

|         | 5.4  | Command Blocks (CB)<br>5.4.1 Interface Command Block (ICB)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-11<br>5-16                                                                                   |

|         | 5.5  | Command Queuing                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-16                                                                                           |

|         | 5.6  | SCSI Protocol<br>5.6.1 WD7000-ASC Supported Messages                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-17<br>5-17                                                                                   |

|         | 5.7  | Exception Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-18                                                                                           |

#### SECTION 6 COMMANDS PAGE 6.0 General 6-1 6.1 Command Port Control Opcodes 6-1 6.1.1 No Operation (00) 6-2 6.1.2 Initialization (01) 6-2 Disable Unsolicited Interrupts 6.1.3 (02)6-3 6.1.4 Enable Unsoliocited Interrupts (03)6-3 6.1.5 Interrupt On Free OGMB (04) 6-3 6.1.6 Start Command (80 - BF) 6-3 Start Multiple I/O (CO - FF) 6.1.7 6-4 6.2 WD7000-ASC Commands (ICB) 6-4 6.2.1 Open Receive Buffer (80) 6-5 6.2.2 Receive Command (81) 6-6 6.2.3 Receive Data (82) 6-7 Receive Data With Status 6.2.4 (83) 6-8 6.2.5 Send Data (84) 6-8 6.2.6 Send Data With Status (85) 6-9 6-10 6.2.7 Send Status (86) Read Initilization Bytes (88) 6.2.8 6-11 6.2.9 Read WD7000-ASC Device Address 6-11 6.2.10 Set Unsolicited Interrupt Mask (8A) 6-12 6.2.11 Read Unsolicited Interrupt Mask (8B) 6-13 6.2.12 Read Firmware Revision Level (8C) 6-15 6.2.13 Execute Diagnostics (8D) 6-16 6.2.14 Set Execution Parameters (8E) 6-17 6.2.15 Read Execution Parameters (8F) 6-17 6.3 Vendor Unique Error Codes 6-17

|  | PAGE |

|--|------|

| SECTION | 7 T | IMING      |                  |             | PAGE |

|---------|-----|------------|------------------|-------------|------|

|         | 7.0 | General    |                  |             | 7-1  |

|         | 7.1 | Electrical | Specifications   |             | 7-1  |

|         |     | 7.1.1 D.C  | Characteristics  | 3           | 7-1  |

|         |     | 7.1.2 A.C  | Characteristics  | 5           | 7-2  |

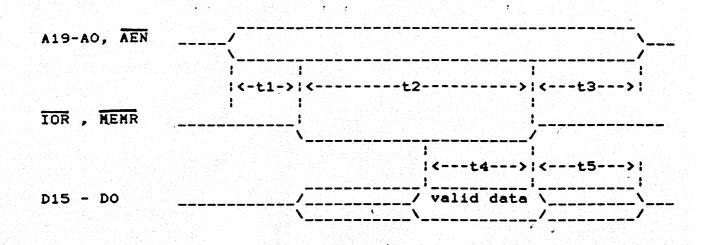

|         |     | 7.1.2.1    | Host Programmed  | I/O or BIOS |      |

|         |     |            | ROM Read         |             | 7-2  |

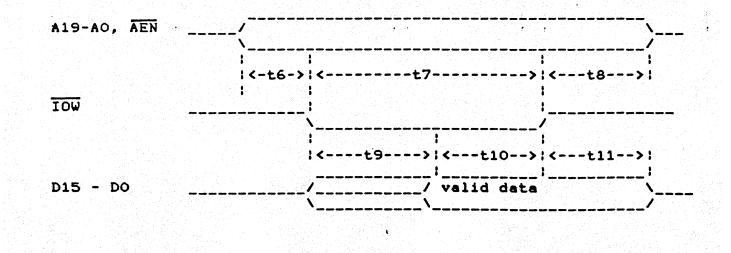

|         |     | 7.1.2.2    | Host Programmed  | I/O Write   | 7-3  |

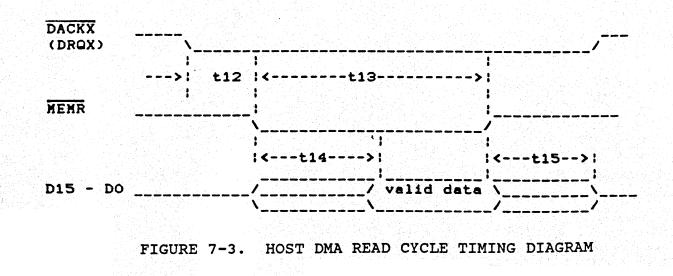

|         |     |            | Host DMA Read Cy |             | 7-4  |

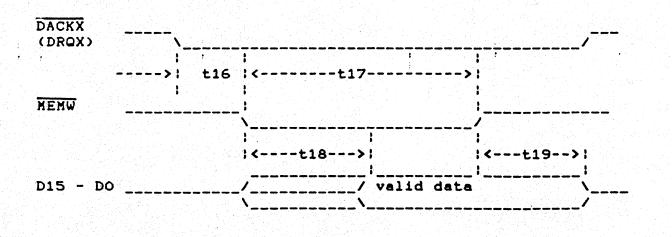

|         |     |            | Host DMA I/O Wr  |             | 7-5  |

## LIST OF TABLES

| TABLE                                                       | TITLE                                                                                                                                                                                                                                                                                 | PAGE                                                     |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 3-1                                                         | WD7000-ASC Jumper Configurations                                                                                                                                                                                                                                                      | 3-3                                                      |

| 4-1                                                         | Pl Connector Pin Outs                                                                                                                                                                                                                                                                 | 4-2                                                      |

| 4-2                                                         | P2 Connector Pin Outs                                                                                                                                                                                                                                                                 | 4-3                                                      |

| 4-3                                                         | SCSI Interface Connector Pin Outs                                                                                                                                                                                                                                                     | 4-8                                                      |

| 4-4                                                         | Floppy Disk Drive Connector Pin Outs                                                                                                                                                                                                                                                  | 4-9                                                      |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9 | WD7000-ASC I/O Port Definition<br>WD7000-ASC Status Byte Format<br>Interrupt Status Byte/Diagnostic Error Code<br>Host Control Byte Format<br>Mail Box Format<br>ICMB Return Status Byte Values<br>SCSI Command Block<br>ICB Command Execution Block<br>WD7000-ASC Supported Messages | 5-4<br>5-6<br>5-7<br>5-9<br>5-11<br>5-12<br>5-16<br>5-18 |

| 6-1                                                         | WD7000-ASC Command Port Opcodes                                                                                                                                                                                                                                                       | 6-1                                                      |

| 6-2                                                         | Initialization Command Format                                                                                                                                                                                                                                                         | 6-3                                                      |

| 6-3                                                         | ICB Command Opcodes                                                                                                                                                                                                                                                                   | 6-5                                                      |

| 6-4                                                         | Open Receiver Buffer ICB Format                                                                                                                                                                                                                                                       | 6-6                                                      |

| 6-5                                                         | Receive Command ICB Format                                                                                                                                                                                                                                                            | 6-7                                                      |

| 6-6                                                         | Receive Data ICB Format                                                                                                                                                                                                                                                               | 6-7                                                      |

| 6-7                                                         | Receive Data With Status ICB Format                                                                                                                                                                                                                                                   | 6-8                                                      |

| 6-8                                                         | Send Data ICB Format                                                                                                                                                                                                                                                                  | 6-9                                                      |

| 6-9                                                         | Send Data With Status ICB Format                                                                                                                                                                                                                                                      | 6-10                                                     |

| 6-10                                                        | Send Status ICB Format                                                                                                                                                                                                                                                                | 6-10                                                     |

| 6-11                                                        | Read Initialization Bytes ICB Format                                                                                                                                                                                                                                                  | 6-11                                                     |

| 6-12                                                        | Read Initialization Bytes ICB Format                                                                                                                                                                                                                                                  | 6-12                                                     |

| 6-13                                                        | Set Unsolicited Interrupt Mask ICB Format                                                                                                                                                                                                                                             | 6-13                                                     |

| 6-14                                                        | Read Unsolicited Interrupt Mask ICB Format                                                                                                                                                                                                                                            | 6-14                                                     |

| 6-15                                                        | Read Firmware Revision Level (8C)                                                                                                                                                                                                                                                     | 6-15                                                     |

| 6-16                                                        | Execute Diagnostics ICB Format                                                                                                                                                                                                                                                        | 6-16                                                     |

| 7-1                                                         | D.C. Characteristics                                                                                                                                                                                                                                                                  | 7-1                                                      |

| 7-2                                                         | Host Programmed I/O or BIOS ROM Read Parameters                                                                                                                                                                                                                                       | 7-3                                                      |

| 7-3                                                         | Host Programmed I/O Write Parameters                                                                                                                                                                                                                                                  | 7-4                                                      |

| 7-4                                                         | Host DMA Read Cycle Timing Parameters                                                                                                                                                                                                                                                 | 7-5                                                      |

| 7-5                                                         | Host DMA I/O Write Cycle Timing Parameters                                                                                                                                                                                                                                            | 7-6                                                      |

## LIST OF ILLUSTRATIONS

| FIGURE     | TITLE                                                                                              | PAGE         |

|------------|----------------------------------------------------------------------------------------------------|--------------|

| 1-1        | WD17000-ASC Host Bus Adapter Block Diagram                                                         | 1-1          |

| 3-1        | WD7000-ASC Board Connectors and Jumper Locations                                                   | 3-2          |

| 5-1<br>5-2 | Execution of SCB/ICB<br>Completion of SCB/ICB                                                      | 5-14<br>5-15 |

| 7-1<br>7-2 | Host Programmed I/O or BIOS ROM Read Timing<br>Diagram<br>Host Programmed I/O Write Timing Diagram | 7-2<br>7-3   |

| 7-3<br>7-4 | Host DMA Read Cycle Timing Diagram<br>Host DMA I/O Write Cycle Timing Diagram                      | 7-4<br>7-5   |

#### SECTION 1

#### INTRODUCTION

#### 1.0 DOCUMENT SCOPE

This document describes the design and performance of the WD7000-ASC Host Bus Adapter. The user is encouraged to become familiar with the following related documents:

| WD33C93         | . SCSI Bus Interface Controller Data Sheet  |

|-----------------|---------------------------------------------|

|                 | Floppy Disk Subsystem Controller Data Sheet |

| SCSI            | ANSI Standard Specification X3T9.2          |

| IBM AT          | IBM AT Technical Reference Manual           |

| Z80 • • • • • • | Zilog Technical And Programming Manuals     |

#### 1.1 DESCRIPTION

The WD7000-ASC is an interface channel between the IBM AT bus and the SCSI bus. All the necessary drivers and receivers are included. Direct cable connections to the SCSI bus are made possible through a 50 pin connector. The IBM AT interface is made through two card edges as defined by the IBM AT Technical Manual. Address space, DMA channels, and interrupt requests can be selected to suit the user's application by optional jumper configurations.

To facilitate data transfer between the IBM AT and SCSI buses, the WD7000-ASC contains an onboard CPU (Z80) and a 16 byte FIFO on the IBM AT bus to maintain a 2.5 Mbyte/sec synchronous SCSI data transfer rate with the WD33C93, or a 4.0 Mbyte/sec synchronous SCSI data transfer rate with the WD33C93A. First Party DMA Logic (FPDMA) is employed to handle most of the command, data and status information via an outgoing mail box system, so that several logical units can be connected simultaneously. All other handshaking required to transfer data is done by the local CPU (LCPU).

The SCSI interface consists of the WD33C93 SCSI Bus Interface Controller (SBIC) that handles all of the arbitration, selection, disconnection, and reselection, leaving the LCPU to manage data transfers more efficiently. The SBIC is usually configured to operate as the initiator but can operate as a target as well in a multi-initiator system. Selection as a target generates an unsolicited interrupt to the Host IBM AT computer, if so enabled by the Host. Further communication is controlled totally by the Host IBM AT system, with the LCPU managing all of the required handshaking between the SBIC and the Host CPU.

1-1

An onboard floppy disk subsystem controller and a BIOS ROM are provided for the convenience of the Host. The WD37C65 Floppy Disk Subsystem Controller supports two floppy and is controlled entirely by the Host CPU. The BIOS ROM enables the Host to boot off a SCSI drive if desired.

The WD7000-ASC supports the common command set including all of the extended SCSI commands. SCSI commands are queued by the WD7000-ASC and can be linked by any initiator in the system. The SCSI bus parity option is fully supported as well. The onboard diagnostic capability allows field replacements easily and quickly.

The WD7000-ASC is based on a proprietary chip set specifically designed to add an SCSI port to the IBM AT bus.

## 1.2 FEATURES

- O INTELLIGENT Z80 CPU CHANNEL CONTROL

- o WD37C65 FLOPPY DISK CONTROLLER

(OPTIONAL)

- O BIOS ROM (OPTIONAL)

- O WD33C93 SBIC FOR SCSI INTERFACE

- O FIRST PARTY DMA DATA TRANSFERS

- O ANY BLOCK SIZE TRANSFERS UP TO 16 MBYTES

- O EVEN OR ODD DMA START ADDRESS

- O 16 BYTE FIFO ON AT BUS

- USER SELECTABLE DEVICE ADDRESS, DMA AND INTERRUPT CHANNELS

- o 4.0 MB/SEC SCSI SYNCHRONOUS DATA

TRANSFER RATE\*

- O 2.0 MB/SEC SCSI ASYNCHRONOUS DATA TRANSFER RATE

- MULTIPLE LOGICAL THREAD CONNECTIONS UP TO 16 UNITS

- \* 4.0 MB/SEC WITH WD33C93A 2.0 MB/SEC WITH WD33C93

- O OPERATES AS INITIATOR OR TARGET

- O BUS ARBITRATION INCLUDING DIS-CONNECT AND RECONNECT

- STANDARD AND EXTENDED SCSI COM-MANDS

- O SUPPORTS FULL SCSI COMMAND SET

- O SCSI BUS PARITY OPTION

- O QUEUED SCSI COMMANDS

- O PROGRAMMABLE DMA BUS ON/OFF TIMES

- O LINKED SCSI COMMANDS

- O ONBOARD CONTROLLER DIAGNOSTICS

- O IBM AT FORM FACTOR

- O SINGLE +5V POWER SUPPLY

#### 1.3 <u>OPERATION</u>

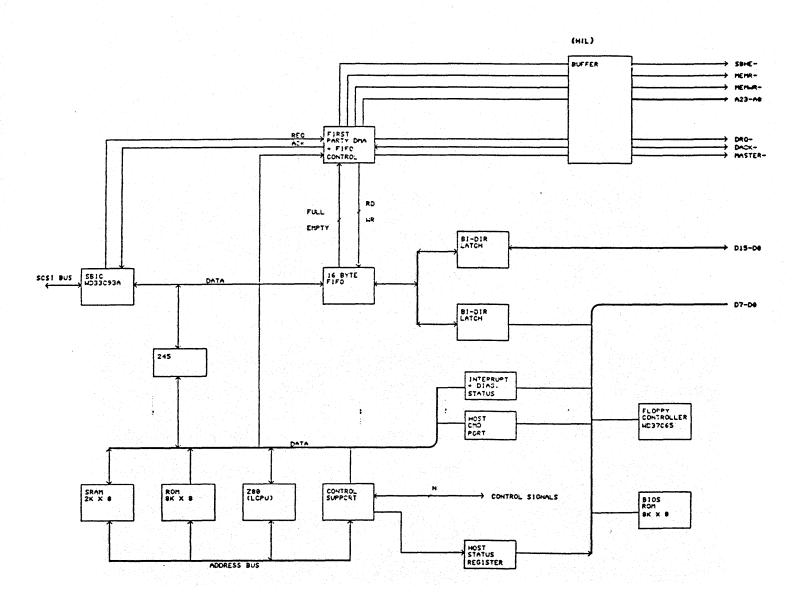

This section provides an operational overview of the WD7000-ASC Host Bus Adapter. Figure 1-1 illustrates the WD7000-ASC Host Bus Adapter block diagram with the major functional blocks. The major functional blocks are:

- o Local Microprocessor (LCPU)

- o Program Memory (ROM)

- o Scratchpad RAM (SRAM)

- o First Party DMA Logic (FPDMA)

- o Host Interface Logic (HIL)

- o SCSI Bus Interface Controller (SBIC)

- o Floppy Disk Subsystem Controller (FDC)

- O BIOS ROM (BIOS)

- o Control Support Logic (CS)

### 1.3.1 LOCAL MICROPROCESSOR (LCPU)

The Local Microprocessor (LCPU) is a Zilog Z80, the heart of the control logic for the WD7000-ASC. By interpreting commands sent from the Host, the LCPU configures the other logic blocks to perform the desired operation. This includes setting the data transfer direction, DMA starting address, time on and time off the IBM AT bus counters, as well as control of the SBIC.

Host access to the WD7000-ASC via the command port causes the LCPU to read the command byte immediately. The command is decoded and either executed if it is an ASC local command or put in the SBIC queue if it is meant for a SCSI device. In all cases, the Host is informed within 70uS whether the command has been accepted or not by the WD7000-ASC.

The actual execution time for a particular command, that has been put in a queue, is governed by: the programmed DMA bus on/off times, the number of mail boxes available, the length of the data transfers, and any exception handling involved.

- 김 사람은 것이 많은 것이 많은 것이 없는 것이다.

FIGURE 1-1. WD7000-ASC HOST BUS ADAPTER BLOCK DIAGRAM

## 1.3.1.1 LCPU CLOCK

The LCPU uses a 4 MHz clock obtained by dividing the 8 MHz clock used for the SBIC device. This gives the LCPU a basic clock period of 250nS referred to as the T cycle. The machine cycles vary from 4 to 23 T states. A complete description of the instruction set and execution times can be found in the references listed in the front of this Section.

#### 1.3.2 PROGRAM MEMORY

The Program Memory (ROM) is an 8K X 8 PROM that contains the control firmware for the LCPU with a provision for up to 32K with small changes in the hardware design for any future enhancements. The other 32K of the address space, differentiated by Al5, is reserved for data memory.

#### 1.3.3 SCRATCHPAD RAM

The Scratchpad RAM (SRAM) is 2K X 8 and is used by the LCPU to store variables and queued commands issued by the Host. Since SCSI command data is directly passed between the Host and the SBIC, no provision has been made to buffer any data, eliminating any latencies required to store and then transfer the data.

The present RAM size is sufficient to handle 16 logical threads which implies that up to 16 commands for different SCSI LUNS can be active at any given instant of time. In addition, the SCAN MAIL BOX command can be used to issue more than 16 commands without requiring any further Host intervention than simply issuing the command. However, more logical threads can be supported by increasing the size of the Scratchpad RAM depending upon future applications at the cost of minor hardware modifications.

#### 1.3.4 FIRST PARTY DMA LOGIC

First Party DMA Logic (FPDMA) provides high speed data transfers by allowing the WD7000-ASC to be master of the IBM AT bus. The hardware consists of a 16 byte FIFO that can transfer a word across the AT bus every 375nS, DMA control logic to transfer data in word mode or byte mode, on even or odd addresses, and a 24-bit counter to address up to 16M of Host memory. The bus on/off times are fully programmable by the Host. The DMA state machine control is implemented using PALS as described in the referencess listed in the front of this Section. The LCPU sets data transfer direction, starting DMA address, time on and time off the AT bus and then issues a START. For WD7000-ASC to AT transfers, the FPDMA will wait for data to be filled in the FIFO, then arbitrate for the AT bus by asserting DRQ. Upon receiving DACK the FPDMA will assert MASTER and then start writing to the AT's memory. The FPDMA will continue as master until time on the bus is exhausted or FIFO is empty. It will stay off the bus until the time off the bus is exhausted then re-arbitrate if data is still in the FIFO. AT to WD7000-ASC transfers are similiar except reads are done from the AT's memory and data is stored in the FIFO. The WD7000-ASC will continue to re-arbitrate for the bus until all data has been transferred across the FIFO.

The FPDMA also provides the necessary signals to transfer data between the SBIC and FIFO and between the LCPU and FIFO.

### 1.3.5 HOST INTERFACE LOGIC

The Host Interface Logic (HIL) contains the requisite logic to buffer all data and control between the IBM AT bus and the WD7000-ASC. The Host interface consists of 16 data lines, a 24-bit address bus and control lines. For a description of the signals and pinouts refer to Section 4. HIL also contains a: Command Register, WD7000-ASC Interrupt Strobe, Static Reset, and an SCSI Bus Reset.

#### 1.3.6 SCSI BUS INTERFACE CONTROLLER

The SCSI Bus Interface Controller (SBIC) is a single chip SCSI controller that can operate either as a target or an initiator. When the SBIC status register indicates reselection, it is configured as the initiator. If the selection status is set, then it is configured as a target. The SBIC, under the control of the LCPU, generates all of the necessary signals and timing to command the SCSI bus and transfer information across it.

## 1.3.7 FLOPPY DISK SUBSYSTEM CONTROLLER

The Floppy Disk Subsystem Controller (FDC) is a single chip floppy disk controller. With minimal hardware it interfaces directly to the IBM AT bus and enables the Host to control up to two drives.

## 1.3.8 BIOS ROM

The BIOS ROM (BIOS), consisting of an 8K X 8 ROM, enables the Host to boot directly from a hard disk drive on the SCSI bus and to determine the number of logical units connected to the bus at power on. The other main function is to convert the Host DOS interrupt 13 protocol to the mail box protocol, including the SCSI CDB construction.

The address space of the BIOS is configurable in the range COXXX-DEXXX (Hex), with the LSB 13 bits being used to address the 8K ROM.

#### 1.3.9 CONTROL SUPPORT LOGIC

The Control Support Logic (CS) consists mainly of decoders in the I/O address space of the LCPU, the reset circuitry, miscellaneous combination logic and memory elements needed to control the various functional blocks. Due to the nature of the CS, Control Support Logic tends to be logically distributed as required instead of being mostly centralized as other blocks. Nevertheless, CS can functionally be thought of as a block that is used by the LCPU to implement all of the real time control functions required to direct the signal flow within the WD7000-ASC channel.

#### 1.3.9.1 RESET LOGIC

The reset pulse for the WD7000-ASC can come from three sources: power-up reset, Host, or the SCSI port.

The reset from the SCSI port is used to reset the SBIC device but not the LCPU. This was done to maintain all of the Host command queue so that these commands can be re-started without having the Host re-issue the commands again.

A similiar set/reset D-FF is provided to reset all of the devices on the SCSI interface. Host access to these two reset registers is explained in Section  $\mathcal{Z}$  along with the other Host addressable WD7000-ASC ports.

## SECTION 2

## SPECIFICATIONS

## 2.0 <u>GENERAL</u>

This section contains the overall specifications for the WD7000-ASC Host Bus Adapter.

## 2.1 PHYSICAL

| Form Factor:<br>Length:<br>Height:<br>Width:                                                                                                                 | IBM PC AT<br>13.1 inches (33.27 centimeters)<br>0.50 inches (1.27 centimeters)<br>4.75 inches (10.67 centimeters)                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 POWER                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                       |

| Voltage:<br>Current:                                                                                                                                         | +5VDC $\pm$ 5%<br>2.0 amps max, 1.7 amps typical                                                                                                                                                                                                                                                                                                      |

| 2.3 PERFORMANCE                                                                                                                                              | 알랐다. 2018년 1월 2019년 1<br>2월 2019년 1월 2019년 1월<br>2월 2019년 1월 2 |

| Host Transfer Rate:<br>SCSI Transfer Rate:<br>LCPU Clock:<br>SBIC Clock:<br>Selection Time Out:<br>Logical Threads:<br>AT Bus On/Off Time:<br>MTBF:<br>MTTR: | <pre>5.3 MByte/sec Burst 4.0 Mbyte/sec Synchronous 2.0 Mbyte/sec Asynchronous 4 MHZ 8 MHZ 250mS 16 Programmable 10,000 POH 30 minutes</pre>                                                                                                                                                                                                           |

2-1

## 2.4 HOST INTERFACE

16-Bit, Bi-directional AT Bus 62 Pin Card Edge Connector 38 Pin Card Edge Connector

2.5 SCSI INTERFACE

9-Bit, Bi-directional SCSI Bus 50 Pin SCSI connector 20 ft.max (6 meters) Drive Cable length

2.6 ENVIRONMENTAL:

Ambient Temperature: Relative Humidity: Air Flow:

Altitude: Altitude: 0°C (32°F) to 55°C (131°F) 10% to 95% non-condensing 100 lin ft/min. at 0.5" from component surface 10,000 ft. max (operating) 15,000 ft. max (storage)

#### SECTION 3

#### INSTALLATION

#### 3.0 GENERAL

This section briefly covers the installation of the WD7000-ASC into an IBM AT computer. Reference should be made to the IBM AT Technical Reference Manual during installation.

#### 3.1 HARDWARE INSTALLATION

Observe the following basic steps while installing the WD7000-ASC Host Bus Adapter:

- 1. Ensure that <u>all</u> electrical power to the computer is OFF.

- 2. Install the WD7000-ASC Host Bus Adapter into the computer chassis.

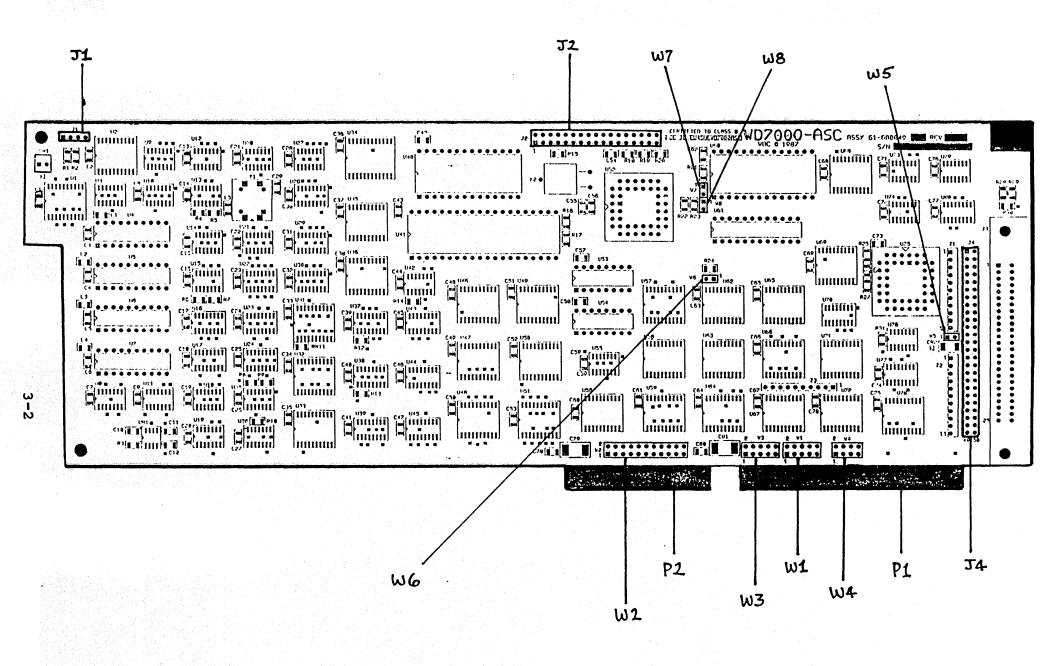

- 3. Refer to Figure 3-1, then connect the 50 pin SCSI interface connector to J4 and the 34 pin disk drive connector to J2. Connect Host furnished power source to J1.

- 4. Power up the computer.

#### 3.2 SOFTWARE INSTALLATION

Refer to the IBM Disk Operating System Manual for complete formatting instructions.

### 3.3 JUMPER CONFIGURATIONS

The various jumper configurations are shown in figure and tables. Installing the jumper in the positions shown will force that option to a logic low level. Removing the jumper from the position shown will force that option to a logic high level.

There are eight jumper locations on the WD7000-ASC Host Bus Adapter: W1, W2, W3, W4, W5, W6, W7, W8. The user may select to change the WD7000-ASC I/O Address Space, the BIOS ROM Address Space, the DMA Channel, the Interrupt Request Channel, Terminator Power, Floppy Controller Deselection, Select one of two speeds for the Floppy Disk Drive, or select the time factor to Write Precompensation for the Floppy Controller.

Table 3-1 presents the WD7000-ASC jumper configurations.

3-1

FIGURE 3-1. WD7000-ASC BOARD CONNECTORS AND JUMPER LOCATIONS

## TABLE 3-1. WD7000-ASC JUMPER CONFIGURATIONS

| W1:<br>IRQ3<br>IRQ4<br>IRQ5<br>IRQ7<br>IRQ9 | 1  <br>3  <br>5  <br>7  <br>9 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 2<br>4<br>6<br>8<br>10 |

|---------------------------------------------|-------------------------------|------------------|------------------|------------------------|

| DRQ/DAC                                     | CK JI                         | MPEI             | RS (V            | <b>12):</b>            |

| W2:                                         |                               |                  |                  | F                      |

| DRQ7                                        | 1                             | 0                | 0                | 2                      |

| DRQ6                                        | 3                             | 0                | 0                | 4                      |

| DRQ5                                        | 5                             | 0                | o                | 6                      |

| DACK7~                                      | 7                             |                  | 0                | 8                      |

| DACK6~                                      | 9                             | 0                | 0                | 10                     |

| DACK5~                                      | 11                            | ō                | 0                | 12                     |

| Direns                                      |                               |                  |                  | <u> </u>               |

| I/O ADI                                     | DRESS                         | S SP             | ACE              | (W3):                  |

| W3:                                         | 4                             |                  |                  | <br>•                  |

| SA3                                         | 1                             | 0                | 0                | 2                      |

| SA4                                         | 3                             | 0-               | 0                | 4                      |

| SA5                                         | 5                             | 0                | 0                | 6                      |

| SA6                                         | 7                             | 0-               | 0                | 8                      |

| SA7                                         | 9                             | 0-               | 0                | 10                     |

|                                             |                               |                  |                  | . – –                  |

+

. .

+

| W2:   | -  | + |   | F  |

|-------|----|---|---|----|

| IRQ15 | 13 | 0 |   | 14 |

| IRQ14 | 15 | 0 | 0 | 16 |

| IRQ12 | 17 | 0 | 0 | 18 |

| IRQ11 | 19 | 0 | 0 | 20 |

| IRQ10 | 21 | 0 | 0 | 22 |

|       | -  | + |   | F  |

| L                                     | L           |     | L        |          |                                                                                                                                                                                                                                                                   | -       |

|---------------------------------------|-------------|-----|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| SA7                                   | SA6         | SA5 | SA4      | SA3      | 1/0                                                                                                                                                                                                                                                               | ADDRESS |

| 1 1                                   | 1           | 1   | 1        | 1        | 3F8                                                                                                                                                                                                                                                               |         |

| 1                                     | 1           | 1   | 1        | 0        | 3F(                                                                                                                                                                                                                                                               |         |

| 1                                     | 1           | 1   | 0        | 1        | 3E8                                                                                                                                                                                                                                                               |         |

| 1                                     | 1           | 1   | 0        | 0        | 3E(                                                                                                                                                                                                                                                               |         |

| 1                                     | 1           | 0   | 1        | 1        | 3D8                                                                                                                                                                                                                                                               |         |

| 1                                     | 1           | 0   | 1        | 0        | 3D                                                                                                                                                                                                                                                                |         |

| 1                                     | 1           | 0   | 0        | 1        | 308                                                                                                                                                                                                                                                               |         |

| 1                                     | 1           | 0   | 0        | 0        | 30                                                                                                                                                                                                                                                                |         |

| ] 1                                   | 0           | 1   | 11       | 1 1      | '3B                                                                                                                                                                                                                                                               |         |

| 1                                     | 0           | 1   | 1        | 0        | 3B                                                                                                                                                                                                                                                                |         |

| 1                                     | 0           | 1   | 0        | 1        | 3A                                                                                                                                                                                                                                                                |         |

| 1                                     | 0           |     | 0        | 1        | 3A                                                                                                                                                                                                                                                                |         |

| 1                                     | 0           | 0   | 1        | 1        | 39                                                                                                                                                                                                                                                                |         |

| 1                                     | 0           | 0   | 1        | 0        | 39                                                                                                                                                                                                                                                                |         |

| 1                                     | 0           | 0   | 0        | 1        | 38                                                                                                                                                                                                                                                                |         |

|                                       | 0           | 0   | 0        | 0        | 38                                                                                                                                                                                                                                                                |         |

| 0                                     | 1<br>  1    | 1   | 1<br>  1 | 1<br>  0 | 37                                                                                                                                                                                                                                                                |         |

|                                       | 1           |     |          |          | 36                                                                                                                                                                                                                                                                |         |

| 0                                     | 1           |     |          |          | 36                                                                                                                                                                                                                                                                |         |

| 0                                     | 1           |     | 1 1      |          | 35                                                                                                                                                                                                                                                                |         |

| 0                                     |             | 0   |          |          | 35                                                                                                                                                                                                                                                                |         |

|                                       | 1           | 0   |          |          | 34                                                                                                                                                                                                                                                                |         |

| 0                                     | ±<br>  1    | 0   | 0        |          | 34                                                                                                                                                                                                                                                                |         |

| 0                                     |             | 1 1 |          |          | 33                                                                                                                                                                                                                                                                |         |

| 0                                     | 0           | 1   | 1 1      | Ō        | 33                                                                                                                                                                                                                                                                |         |

| 0                                     | 0           | 1   | 0        |          | 32                                                                                                                                                                                                                                                                |         |

| i õ                                   | 0           | 1   | 0        | Ō        | 320                                                                                                                                                                                                                                                               |         |

| 0                                     | 0           | ō   | 1        | 1 1      | 31                                                                                                                                                                                                                                                                |         |

| 0                                     | 0           | 0   | 1        | Ō        | 31                                                                                                                                                                                                                                                                |         |

| 0                                     | 0           | 0   | i ō      | 1        | 30                                                                                                                                                                                                                                                                |         |

| 0                                     | i o         | 0   | 0        | Ō        | 30                                                                                                                                                                                                                                                                |         |

| <ul> <li>Anno 1977 (Split)</li> </ul> | • Star 1997 | •   | •        | •        | 5 C (1997) - 1997) - 1997)<br>1997 - 1997 - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1<br>1997 - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1997) - 1 |         |

+

te present Stand Stand

NOTE: A "1" INDICATES NO JUMPER

| 4: ++<br>A13 1   0 0   2                                                              | +       |        |          |       |                |

|---------------------------------------------------------------------------------------|---------|--------|----------|-------|----------------|

|                                                                                       | SA16    | SA15   | SA14     | SA13  | BIOS ADDRESS   |

| A14 3 0 0 4<br>A15 5 0 0 6                                                            | 1       | 1      | 1        | 1     | DEOOH          |

| A16 7   0 0   8                                                                       | 1       | 1<br>1 | 1        | 0     | DCOOH<br>DAOOH |

|                                                                                       |         | 1      | 0        | 0     | DROOH          |

|                                                                                       | 11      | Ō      | 1        | 1     | D600H          |

|                                                                                       | 11      | 0      | 1        | 0     | D400H          |

|                                                                                       | 1       | 0      | 0        | 1     | D200H          |

|                                                                                       | 1       | 0      | 0        | 0     | D000H          |

|                                                                                       | 0       | 1      | 1<br>  1 | 1     | СЕООН<br>ССООН |

|                                                                                       |         | 1<br>1 |          | 0     | CA00H          |

|                                                                                       |         | i      | 0        | ō     | C800H          |

|                                                                                       | 0       | 0      | 1        | 1     | C600H          |

|                                                                                       | 0       | 0      | 1        | 0     | C400H          |

|                                                                                       | 0       | 0      | 0        | 1     | C200H          |

|                                                                                       | 0       | 0      | 0        | 0     | СОООН          |

| ERMINATOR POWER (W5):<br>++<br>RMPWR 1   00   2<br>++<br>LOPPY CONTROLLER DESELECTION | (W6):   |        |          |       |                |

| 6: ++<br>SEL 1   00   2<br>++                                                         |         |        |          |       |                |

| UAL SPEED FLOPPY 300/360 RPM<br>7: ++                                                 | (W7):   |        |          |       |                |

| RV 1   0 0   2<br>++                                                                  |         |        |          |       |                |

| RITE PRECOMP FOR FLOPPY CONTRO<br>87NS WITH JUMPER (W8):<br>8: ++                     | OLLER : | 125NS  | WITH     | JUT J | UMPER          |

| CVAL 1 0 0 2                                                                          |         |        |          |       |                |

#### SECTION 4

#### INTERFACE CONNECTORS

## 4.0 <u>GENERAL</u>

The WD7000-ASC has five onboard connectors; two Host interface connectors, a 50 pin SCSI interface connector, a 34 pin connector for the floppy disk drive interface, and a four pin connector for the Host furnished drive select led.

The Host interface connectors provide interface signals that are compatible with the IBM PCAT on the mother board. For a complete description of the interface, reference should be made to the IBM AT Technical Manuals.

The SCSI interface is completely explained in the ANSI Standard X3T9.2 Specifications.

4.1 HOST INTERFACE CONNECTORS (P1, P2)

The Host interface is made through the 62 pin board edge connector (P1), and a 36 pin board edge connector (P2), where the computer I/O bus and power is available to the WD7000-ASC (refer to Figure 3-1). Connector pins Al through A31, and Cl through C18, are located on the component side of the WD7000-ASC. Pins Bl through B31, and Dl through D18 are on the conductor side. The WD7000-ASC does not load the computer I/O bus with more than two LSTTL DC loads per line. The Pl edge connector pin outs are listed in Table 4-1. The P2 edge connector pin outs are listed in Table 4-2. TABLE 4-1. P1 CONNECTOR PIN OUTS

| <u>  I/O PIN</u> | I/O                                     | SIGNAL NAME | L l | I/O PIN | I/0 | SIGNAL NAME |      |

|------------------|-----------------------------------------|-------------|-----|---------|-----|-------------|------|

| Al I             | N/C                                     | IOCHCK      |     | B1      | GND | GND         |      |

| A2               | I/0                                     | D7          |     | B2      | I   | HMR         | 1    |

| A3               | I/O                                     | D6          |     | B3      | +5  | +5VDC       |      |

| A4               | I/0                                     | D5          |     | B4      | 0   | IRQ9        | Í    |

| A5               | I/O                                     | D4          |     | B5      | -5  | -5VDC       | Í    |

| A6               | I/0                                     | D3          |     | B6      | 0   | DRQ2        | Ì    |

| A7               | I/0                                     | D2          |     | B7      | -12 | -12VDC      | , i  |

| A8               | I/0                                     | j Dl        |     | B8      | 0   | OWS         | j    |

| A9               | I/0                                     | DO          |     | B9      | +12 | +12VDC      | Í    |

| A10              | N/C                                     | IOCHRDY     |     | B10     | GND | GND         | 1    |

| A11              | I                                       | AEN         |     | B11     | N/C | SMEMW       | 1    |

| A12              | I/0                                     | A19         |     | B12     | N/C | SMSMR       | Ì    |

| A13              | I/0                                     | A18         |     | B13     | I/0 | IOW         | i    |

| A14              | I/0                                     | A17         |     | B14     | I/0 | IOR         | İ    |

| A15              | I/0                                     | A16         |     | B15     | I   | DACK3       | İ    |

| A16              | I/0                                     | A15         |     | B16     | 0   | DRQ3        | İ    |

| A17              | I/0                                     | A14         |     | B17     | I   | DACKI       | İ    |

| A18              | I/0                                     | A13         |     | B18     | 0   | DRQ1        | , j  |

| A19              | I/0                                     | A12         | 200 | B19     | I/0 | REFRESH     | 1    |

| A20              | I/0                                     | A11         |     | B20     | I   | CLK         | j    |

| A21              | I/0                                     | A10         |     | B21     | 0   | IRQ7        | i I  |

| A22              | I/0                                     | A9          |     | B22     | 0   | IRQ6        | i    |

| A23              | I/0                                     | A8          |     | B23     | 0   | IRQ5        | s j  |

| A24              | I/0                                     | ' A7        |     | · B24   | 0   | IRQ4        | 1    |

| A25              | I/0                                     | A6          |     | B25     | 0   | IRQ3        | j    |

| A26              | I/0                                     | A5          |     | B26     | I   | DACK2       | i    |

| A27              | I/0                                     | A4          |     | B27     | N/C | T/C         | ा    |

| A28              | I/0                                     | A3          |     | B28     | N/C | BALE        | 5 j. |

| A29              | I/0                                     | A2          |     | B29     | +5  | +5VDC       | j    |

| A30              | I/0                                     | A1          |     | B30     | N/C | OSC         | j j  |

| A31              | I/0                                     | A0          |     | B31     | GND | GND         | Ĺ    |

|                  | 2 4 4 5 4 5 4 5 4 5 5 5 5 5 5 5 5 5 5 5 |             | 1 T |         |     |             |      |

### TABLE 4-2. P2 CONNECTOR PIN OUTS

|         |     |             | and the second second second second second second second second second second second second second second second | the second second second second second second second second second second second second second second second s | the second second second second second second second second second second second second second second second se |

|---------|-----|-------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| I/O PIN | I/0 | SIGNAL NAME | I/O PIN                                                                                                          | I/0                                                                                                            | SIGNAL NAME                                                                                                     |

| C1      | I/0 | SBHE        | Dl                                                                                                               | 0                                                                                                              | MEMCS16                                                                                                         |

| C2      | I/0 | LA23        | D2                                                                                                               | 0                                                                                                              | IOCS16                                                                                                          |

| C3      | I/0 | LA22        | D3                                                                                                               | 0                                                                                                              | IRQ10                                                                                                           |

| C4      | I/0 | LA21        | D4                                                                                                               | 0                                                                                                              | IRQ11                                                                                                           |

| C5      | I/0 | LA20        | D5                                                                                                               | 0                                                                                                              | IRQ12                                                                                                           |

| C6      | I/0 | LA19        | D6                                                                                                               | 0                                                                                                              | IRQ15                                                                                                           |

| C7      | I/0 | LA18        | D7                                                                                                               | 0                                                                                                              | IRQ14                                                                                                           |

| C8      | I/O | LA17        | D8                                                                                                               | II                                                                                                             | DACKO                                                                                                           |

| C9      | I/0 | MEMR        | D9                                                                                                               | 0                                                                                                              | DRQO                                                                                                            |

| C10     | I/0 | MEMW        | D10                                                                                                              | j. I                                                                                                           | DACK5                                                                                                           |

| C11     | I/0 | D8          | D11                                                                                                              | 0                                                                                                              | DRQ5                                                                                                            |

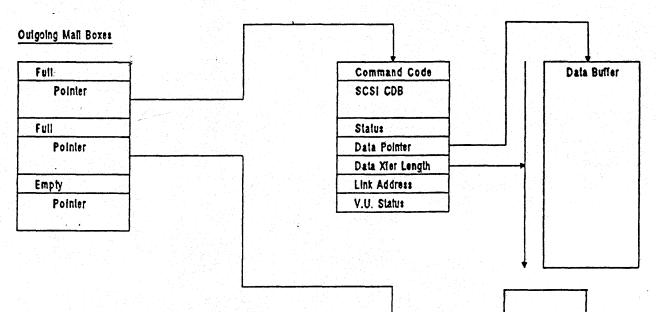

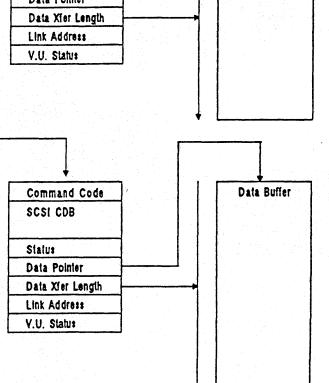

| C12     | I/0 | D9          | D12                                                                                                              | j I                                                                                                            | DACK6                                                                                                           |